?高速DAC輸出后端電路設(shè)計(jì):從芯片選型到系統(tǒng)實(shí)現(xiàn)

發(fā)布時(shí)間:2025-07-07 16:34:09 瀏覽:30

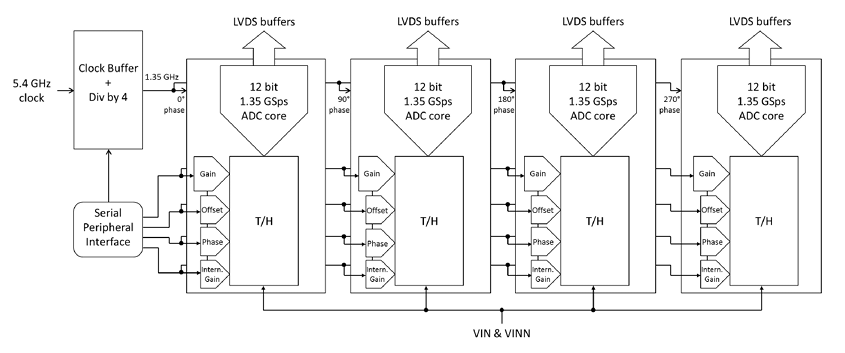

高速DAC(數(shù)字模擬轉(zhuǎn)換器)輸出后端電路設(shè)計(jì)是一個(gè)復(fù)雜且關(guān)鍵的環(huán)節(jié),需要全面權(quán)衡多個(gè)核心要素,包括信號(hào)完整性的保障、精準(zhǔn)阻抗匹配、高效功率傳輸以及有效噪聲抑制等。這一設(shè)計(jì)環(huán)節(jié)的質(zhì)量,直接關(guān)系到高速DAC信號(hào)能否精準(zhǔn)還原,以及其性能能否穩(wěn)定發(fā)揮。

在現(xiàn)代通信、雷達(dá)等對(duì)信號(hào)質(zhì)量要求極為嚴(yán)苛的系統(tǒng)中,高速數(shù)模轉(zhuǎn)換器(DAC)的性能起著決定性作用。它直接影響系統(tǒng)輸出信號(hào)的純凈度、穩(wěn)定性和動(dòng)態(tài)范圍,進(jìn)而對(duì)整個(gè)系統(tǒng)的通信可靠性、目標(biāo)探測(cè)精度等關(guān)鍵指標(biāo)產(chǎn)生重大影響。正因如此,高速DAC輸出后端電路設(shè)計(jì)成為了系統(tǒng)設(shè)計(jì)中的重點(diǎn)與難點(diǎn)所在。

差分轉(zhuǎn)換為單端電路

高速DAC的典型輸出形式為差分電流信號(hào),為了滿足后續(xù)電路的需求,需要借助外部電路將其轉(zhuǎn)換為單端電壓輸出。實(shí)現(xiàn)這一轉(zhuǎn)換的常用方法是使用高速運(yùn)算放大器,例如可選用OPA690高速運(yùn)放芯片來完成電流 - 電壓的轉(zhuǎn)換任務(wù)。

電流 - 電壓轉(zhuǎn)換電路

為了方便后續(xù)的信號(hào)處理,通常會(huì)利用電阻將電流信號(hào)轉(zhuǎn)換為電壓信號(hào)。在這個(gè)過程中,放大電路一般由差分電路構(gòu)成,差分電路能夠把DAC輸出的差分信號(hào)轉(zhuǎn)換為單端輸出信號(hào),從而為后續(xù)處理提供合適的信號(hào)形式。

版圖設(shè)計(jì)要點(diǎn)

版圖設(shè)計(jì)對(duì)于高速DAC輸出后端電路的性能至關(guān)重要。在設(shè)計(jì)版圖時(shí),要求整體布局呈現(xiàn)軸對(duì)稱和中心對(duì)稱的形態(tài)。這種設(shè)計(jì)方式具有多方面優(yōu)勢(shì),一方面能夠簡(jiǎn)化布局布線的過程,提高設(shè)計(jì)效率;另一方面可以有效消除一些具有對(duì)稱性的工藝誤差,對(duì)提升電路性能有顯著益處。

數(shù)字與模擬區(qū)域隔離

由于數(shù)字電路和模擬電路之間存在串?dāng)_和襯底噪聲等問題,為了減少這些干擾對(duì)電路性能的影響,必須對(duì)數(shù)字地和模擬地進(jìn)行分離處理。同時(shí),數(shù)字區(qū)域和模擬區(qū)域之間要保持足夠的距離,在必要時(shí)還可以采用guardring進(jìn)行保護(hù),進(jìn)一步降低噪聲干擾。

后仿真流程

在完成版圖設(shè)計(jì)后,需要先通過DRC(設(shè)計(jì)規(guī)則檢查)和LVS(版圖與原理圖對(duì)比)檢查,確保版圖設(shè)計(jì)符合相關(guān)規(guī)范和要求。之后,使用Calibre等工具進(jìn)行后仿真,通過后仿真可以預(yù)測(cè)芯片的實(shí)際測(cè)試結(jié)果。根據(jù)仿真結(jié)果對(duì)版圖設(shè)計(jì)進(jìn)行調(diào)整和優(yōu)化,能夠有效提高流片的成功率,降低研發(fā)成本和風(fēng)險(xiǎn)。

性能優(yōu)化措施

在版圖布局布線階段,需要充分考慮如何減小耦合影響。耦合效應(yīng)可能會(huì)導(dǎo)致信號(hào)干擾和性能下降,通過合理的布局布線設(shè)計(jì),可以有效降低耦合影響,從而優(yōu)化DAC的性能,確保其能夠穩(wěn)定、高效地工作。

校準(zhǔn)技術(shù)的應(yīng)用

為了有效解決上述在設(shè)計(jì)過程中遇到的各種問題,可以采用校準(zhǔn)技術(shù)。校準(zhǔn)技術(shù)具有諸多優(yōu)勢(shì),它既能夠在保證電路高精度的前提下,減小電流源矩陣在DAC中所占的面積,降低芯片成本;又能緩解電路對(duì)版圖和工藝的嚴(yán)格要求,提高電路的兼容性和可制造性。

綜上所述,高速DAC輸出后端電路設(shè)計(jì)涵蓋了多個(gè)關(guān)鍵環(huán)節(jié)和技術(shù)要點(diǎn)。只有全面考慮這些因素,并采用科學(xué)合理的設(shè)計(jì)方法和優(yōu)化策略,才能設(shè)計(jì)出高性能、高可靠性的高速DAC輸出后端電路,滿足現(xiàn)代通信、雷達(dá)等系統(tǒng)對(duì)信號(hào)質(zhì)量的嚴(yán)格要求。

深圳市立維創(chuàng)展科技是EUVIS的代理經(jīng)銷商,主要提供EUVIS的全球頂尖的高速數(shù)模轉(zhuǎn)換DAC、直接數(shù)字頻率合成器DDS、復(fù)用DAC的芯片級(jí)產(chǎn)品,以及高速采集板卡、動(dòng)態(tài)波形發(fā)生器等產(chǎn)品,原裝現(xiàn)貨,價(jià)格優(yōu)勢(shì),歡迎咨詢。