減小DAC(數模轉換器)電路的耦合影響是確保信號精度和穩定性的關鍵,尤其在高頻、高分辨率或低噪聲應用中。耦合影響可能來自電源噪聲、數字信號干擾、地線回路或寄生參數等。以下是系統化的解決方案:

一、電源設計優化

獨立電源軌

為DAC的模擬部分(如參考電壓、輸出緩沖器)和數字部分(如時鐘、控制邏輯)提供獨立的低噪聲LDO(低壓差線性穩壓器)或線性電源,避免數字開關噪聲通過電源耦合到模擬信號。

示例:使用TPS7A4700(模擬)和TPS7A3301(數字)為DAC供電,兩者均具有超低噪聲(<4μVrms)和高PSRR(電源抑制比)。

電源去耦與濾波

在DAC電源引腳附近放置多層陶瓷電容(0.1μF~10μF)和鉭電容(10μF~100μF),形成寬頻帶去耦網絡,抑制高頻噪聲。

對參考電壓源(VREF)添加RC濾波器(如10Ω電阻+10μF電容),進一步降低紋波。

二、地線布局與隔離

星形接地(Star Grounding)

將模擬地(AGND)、數字地(DGND)和電源地(PGND)在單點連接(通常靠近DAC的AGND引腳),避免地線回路形成。

關鍵點:確保所有模擬信號的地回路盡可能短,直接返回至星形接地點。

分割地平面與跨接

在多層PCB中,將模擬地和數字地平面分開,通過磁珠或0Ω電阻在單點跨接,減少高頻噪聲耦合。

避免:在高頻信號(如時鐘)下方切割地平面,以防阻抗突變引發信號反射。

三、信號完整性設計

數字信號隔離

對DAC的控制信號(如SPI時鐘、數據輸入)使用緩沖器(如74LCX系列)或磁耦合隔離器(如ADuM1401),切斷數字噪聲傳播路徑。

示例:在SPI接口中,通過磁隔離器將數字控制器與DAC隔離,同時保持信號同步。

模擬信號屏蔽與走線

模擬輸出信號線應遠離數字信號線,并采用屏蔽電纜或內層走線(如PCB內層微帶線)。

關鍵參數:保持模擬信號線與數字信號線的間距≥3倍線寬,或通過地線隔離。

四、參考電壓與輸出緩沖優化

低噪聲參考源

選擇超低噪聲參考電壓芯片(如ADR45xx系列,噪聲密度<0.5μVpp/√Hz),并添加RC濾波器進一步衰減高頻噪聲。

示例:ADR4525(2.5V參考)配合10Ω電阻和10μF電容,可抑制>100kHz的噪聲。

輸出緩沖器設計

若DAC輸出直接驅動負載,需在輸出端添加低噪聲運算放大器(如OPA827)作為緩沖器,隔離負載變化對DAC內部電路的影響。

配置:緩沖器采用同相放大器結構,增益為1,以最小化相位延遲。

五、PCB布局與寄生參數控制

關鍵元件布局

將DAC芯片、參考電壓源、去耦電容和輸出緩沖器集中放置,縮短關鍵信號路徑。

示例:DAC芯片與參考電壓源的距離應<5mm,以減少寄生電感。

寄生參數抑制

避免在DAC輸出端使用長走線或過孔,防止寄生電感與電容形成諧振回路。

仿真工具:使用SI/PI仿真軟件(如ADS、HyperLynx)分析寄生參數對信號質量的影響,優化布局。

六、屏蔽與濾波技術

電磁屏蔽

對敏感模擬電路部分(如DAC輸出級)使用金屬屏蔽罩,接地至模擬地平面,屏蔽外部電磁干擾。

材料選擇:采用銅或鋁屏蔽罩,厚度≥0.2mm,以有效衰減高頻噪聲。

濾波器設計

在DAC輸出端添加低通濾波器(如LC或π型濾波器),衰減高頻噪聲和諧波。

參數計算:根據信號帶寬選擇截止頻率,例如對于音頻DAC(20Hz~20kHz),截止頻率可設為100kHz。

七、軟件與算法補償

數字預失真(DPD)

通過軟件算法對DAC輸入信號進行預處理,補償非線性失真和耦合噪聲。

示例:在通信系統中,使用DPD算法抵消DAC輸出端的諧波失真,提高信噪比(SNR)。

動態校準

定期對DAC輸出進行校準(如通過ADC反饋閉環),補償溫度漂移和長期穩定性問題。

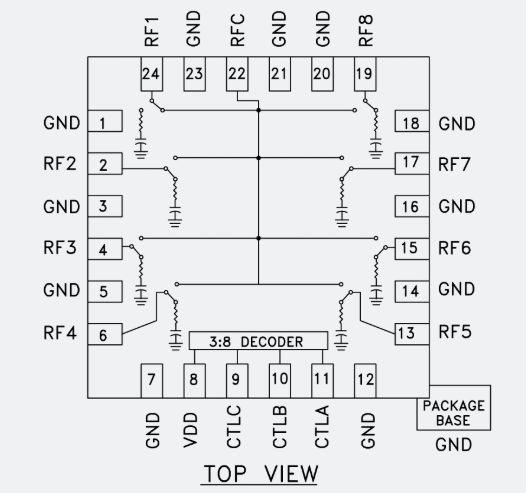

深圳立維創展科技是Teledyne E2V的經銷商,主要供給Teledyne E2V模數轉換器和半導體,可為客戶提供 Teledyne E2V全系列 DAC(含宇航級篩選)的選型、評估板及技術支持。價格優勢,歡迎咨詢。